# KARNA TAKA STATE OPEN UNIVERSITY MUKTHAGANGOTRI, MYSORE- 570 006

DEPARTMENT OF STUDIES IN INFORMATION TECHNOLOGY

C IN INFORMATION SCIENCE

# COMPUTER ORGANIZATION

IS 2.1 BLOCK 1 TO 4

# IS 2.1 Computer Organization

# Preface

This material is prepared to give an overview of Computer Organization for the Second Semester course in M.Sc. (IT) curricula. It is suitable for both hardware and software-oriented students. To study the design details of computer organization and the various concepts related to computer organization, this material has been prepared. The whole material is organized into four modules each with four units. Each unit lists out the objectives of study along with the relevant questions and suggested reading to better understand the concepts.

**Module-1:** Gives an introduction to computer organization. It starts with components of computer, computer functions, interconnection networks. It also describes main memory operations and addressing modes.

**Module-2:** Introduces the basic processing unit. It starts with some fundamental concepts. It describes movement of data and instructions execution. It also describes performance considerations, hardwired control and microprogrammed control.

**Module-3:** Describes the input-output organization. It discusses different types of accessing I/O devices. It also introduces concepts of interrupts, DMA and I/O hardware.

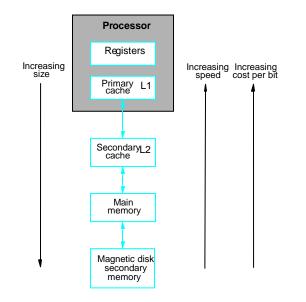

**Module-4**: Introduces the concept of system memory. It starts with basic memory concepts. It explains semiconductor memory chips. It also explains the mechanism of cache memory. It ends with an interesting concept called virtual memory.

We thank everyone who helped us directly or indirectly in preparing this material. Without their support, this material would not have been a reality.

# Karnataka State Open University Mukthagangothri, Mysore – 570 006

Second Semester M.Sc in Information Science Data Base Management Systems

| Module 1 | Introduction to Computer Organization  | Page no |

|----------|----------------------------------------|---------|

| Unit – 1 | COMPUTER ORGANIZATION AND ARCHITECTURE | 06-14   |

| Unit – 2 | COMPUTER STRUCTURES                    | 15-25   |

| Unit – 3 | MAIN MEMORY OPERATIONS                 | 26-37   |

| Unit – 4 | ADDRESSING MODES AND ASSEMBLY LANGUAGE | 38-54   |

|          |                                        |         |

| Module 2 | Basic processing Unit                  |         |

| Unit – 5 | FUNDAMENTAL CONCEPTS                   | 55-68   |

| Unit – 6 | PERFORMANCE CONSIDERATIONS             | 69-76   |

| Unit – 7 | HARD-WIRED CONTROL                     | 77-82   |

| Unit – 8 | MICROPROGRAMMED CONTROL                | 83-104  |

# Module 3 Input-Output Organization

| Unit – 9  | INTRODUCTION TO INPUT/OUTPUT DEVICES     | 105-115 |

|-----------|------------------------------------------|---------|

| Unit – 10 | INTERRUPTS                               | 116-129 |

| Unit – 11 | DIRECT MEMEORY ACCESS                    | 130-139 |

| Unit –12  | I/O HARDWARE AND STANDARD I/O INTERFACES | 140-157 |

| Module 4  | System Memory              |         |

|-----------|----------------------------|---------|

| Unit – 13 | BASIC CONCEPTS             | 158-170 |

| Unit – 14 | SEMICONDUCTOR RAM MEMORIES | 171-191 |

| Unit – 15 | CACHE MEMORIES             | 192-210 |

| Unit – 16 | VIRTUAL MEMORIES           | 211-219 |

| Prof. Vikram Raj Urs                      |

|-------------------------------------------|

| Dean (Academic) & Convener                |

| Karnataka State Open University           |

| Manasagangotri, Mysore – 570 006          |

| Course Co-Ordinator                       |

| Mr. Mahesha DM                            |

| Assistant professor in Computer Science   |

| Dos in Computer Science                   |

| Karnataka State Open University           |

| Manasagangotri, Mysore – 570 006          |

|                                           |

|                                           |

| ogy                                       |

|                                           |

|                                           |

|                                           |

|                                           |

| Dr. Suresh                                |

| professor                                 |

| Department of Studies in Computer Science |

| University of Mysore                      |

| Manasagangothri                           |

|                                           |

|                                           |

|                                           |

|                                           |

|                                           |

# Developed by Academic Section, KSOU, Mysore

Karnataka State Open University, 2012

All rights reserved. No part of this work may be reproduced in any form, by mimeograph or any other means, without permission in writing from the Karnataka State Open University.

Further information on the Karnataka State Open University Programmes may be obtained from the University's Office at Manasagangotri, Mysore - 6.

Printed and Published on behalf of Karnataka State Open University, Mysore-6 by the

# **Registrar** (Administration)

# UNIT 1: COMPUTER ORGANIZATION AND ARCHITECTURE

#### Structure

- 1.0 Objectives

- 1.1 Introduction

- 1.2 Types of computers

- 1.3 Functional units

- 1.4 Basic operational concepts

- 1.5 Definition of computer organization and architecture

- 1.6 Summary

- 1.7 Key words

- 1.8 Answers to check your progress

- 1.9 Unit-end exercises and answers

- 1.10 Suggested readings

# 1.0 **OBJECTIVES**

At the end of this unit you will be able to

- Identify various types of computers

- Identify the functional units of a computer

- State the functions performed by each functional unit

- Discuss the interaction between the CPU and memory

- Understand the difference between Computer organization and architecture

# **1.1 INTRODUCTION**

This unit is about the basic computer organization. It describes what a computer is, its types, its functional components, and how does these functional components work together as a system? It also gives you an overview of the basic operational concepts of computers which involves the functional components such as input, output, memory, arithmetic-logic unit and control unit. We understand the difference between Computer

organization and architecture. The subsequent modules will discuss in detail the organization of each component of the system.

# **1.2 TYPES OF COMPUTERS**

A computer is an electronic device that is capable of accepting data, process the accepted data according to the given sequence of instructions, storing data, presenting data according to given format and communicating data over networks.

There are two broad classes of computers based on the type of input data they accept. They are: Analog Computers and Digital computers.

**Analog Computers:** Electronic devices that are capable of accepting data in analog or time varying form for processing.

**Digital computes:** Electronic devices that are capable of accepting data in the digital form for processing. These computers process the accepted data according to a given sequence of instructions known as a program. The result of processing data is information. The programs and the result reside in the internal storage called computer memory.

Today, there are many types of computers that differ in size, cost, computational power and its indented use. They are:

- Desktops computers

- Portable notebook computers

- Work stations

- Mainframes

- Super computers

#### **Desktops Computers:**

A desktop computer is a personal computer that is designed to be accommodated conveniently on top of a typical office desk. A desktop computer typically consists of various units such as the processor, the display monitor and input devices - usually a keyboard and a mouse that are connected together during installation. Today, almost all desktop computers include a built-in modem, a CD-ROM drive, a multi-gigabyte

magnetic storage drive. In businesses and at home, most desktop computer users can share resources such as printers, plotters and fax machines by getting connected to a local area network.

#### **Portable notebook computers:**

A portable notebook computer is a compact version of a personal computer with all components of a PC packaged into a single unit which is handy and portable. Laptop is an example for this type of computer.

#### Work stations:

A work station is a high computational powered personal computer having high resolution graphics terminals and improved input-output capabilities. It often finds its use in engineering applications and interactive graphics applications.

#### **Mainframes:**

A Main frame computer is a large data processing system used in medium and large sized business units. It is implemented using two or more central processing units and designed to operate at very high speeds for large volumes of data. A Mainframe is also known as an Enterprise system.

#### **Super Computers:**

A super computer is a high-performance computing device meant for highly calculationintensive tasks involving problems on quantum physics, weather forecasting, climate research, molecular modeling and physical simulations such as a rocket design or a submarine design etc.

# **1.3 FUNCTIONAL UNITS**

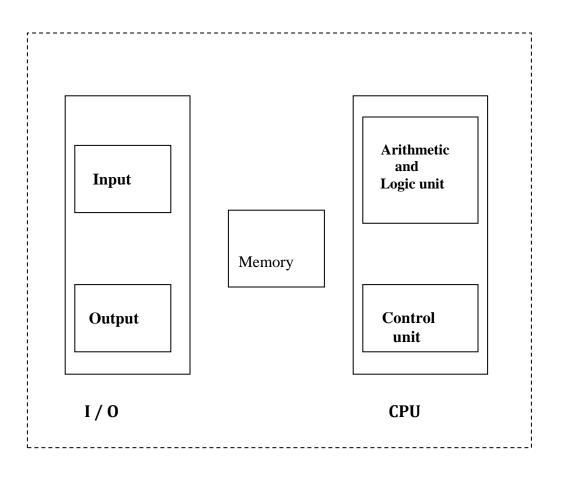

A computer in its simplest form consists of five components. They are: input, output, memory, arithmetic and logic unit, and control unit as shown in the Figure 1.1.

# Figure 1.1 Functional units of a computer

The operations performed by a computer using the functional units can be summarized as follows:

- It accepts information (program and data) through input unit and transfers it to the memory

- Information stored in the memory is fetched, under program control, into an arithmetic and logic unit for processing

- Processed information leaves the computer through an output unit

- The control unit controls all activities taking place inside a computer.

# 1.4 BASIC OPERATIONAL CONCEPTS

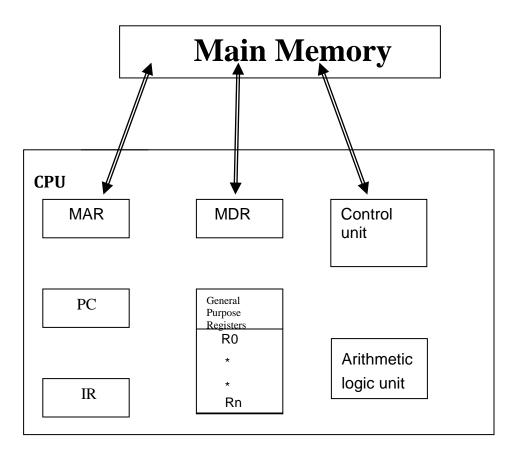

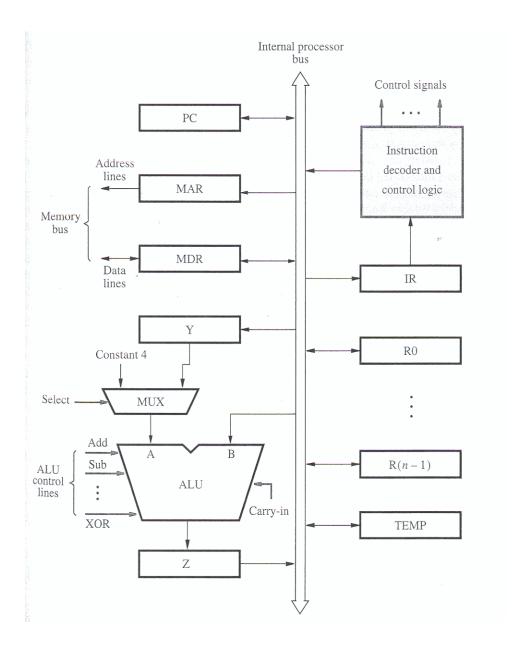

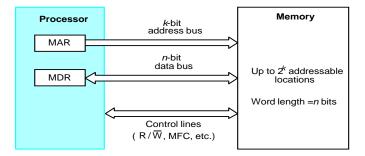

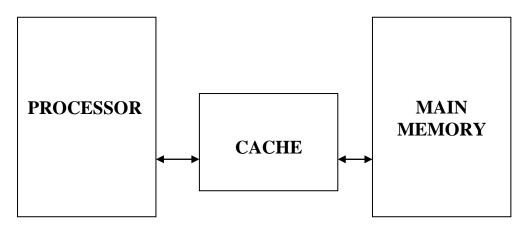

A program is nothing but sequence of instructions that instruct the computer to perform some specified operation on given data. Programs reside in the main memory of the computer. In-order to perform the specified operations, the instructions are brought from memory into the processor. The Figure 1.2 describes the connections between the CPU and the main memory. The processor contains arithmetic and logic unit as the main processing unit, the control unit to control and coordinate all activities in the system. It also contains a number of registers used for various purposes (e.g., temporary storage of data), such as the Instruction Register (IR), the Program Counter (PC), the Memory Address Register (MAR), Memory Data Register (MDR), and the general-purpose registers.

Figure 1.2 Connections between the CPU and the main memory.

**Instruction Register (IR):** contains the instruction that is currently being executed. Its output is available to the control circuit that generates the timing signals for control of the actual processing circuit needed to execute the instruction.

**Program Counter (PC):** is a register that contains the memory address of the instruction currently being executed. During the execution of the current instruction, the content of program counter is updated to correspond to the address of the next instruction.

**Memory Address Register (MAR):** holds the address of the memory location to or from which data is to be transferred.

**Memory Data Register (MDR):** contains the data to be written into or read-out of the addressed memory location.

General-purpose Registers: are used for holding data, intermediate results of operations. They are also known as scratch-pad registers.

Let us consider some typical operating steps involving instruction fetch and execution:

# **INSTRUCTION FETCH**

- Program gets into the memory through an input device

- Execution of a program starts by setting the PC to point to the first instruction of the program.

- The contents of PC are transferred to the MAR and a Read control signal is sent to the memory

- The addressed word (here it is the first instruction of the program) is read out of memory and loaded into the MDR

- The contents of MDR are transferred to the IR for instruction decoding

# **INSTRUCTION EXECUTION**

- The operation field of the instruction in IR is examined to determine the type of operation to be performed by the ALU

- The specified operation is performed by obtaining the operand(s) from the memory locations or from GP registers.

- Fetching the operands from the memory requires sending the memory location address to the MAR and initiating a Read cycle.

- The operand is read from the memory into the MDR and then from MDR to the ALU.

- The ALU performs the desired operation on one or more operands

fetched in this manner and sends the result either to memory location or to a GP register.

- The result is sent to MDR and the address of the location where the result is to be stored is sent to MAR and Write cycle is initiated.

Thus, the execute cycle ends for the current instruction and the PC is incremented to point to the next instruction for a new fetch cycle.

#### **1.5 DEFINITION OF COMPUTER ORGANIZATION AND ARCHITECTURE**

Computer architecture refers to those attributes of a system visible to a programmer, or put another way, those attributes that have a direct impact on the logical execution of a program. Computer organization refers to the operational units and their interconnection that realize the architecture specification. For examples, architecture attributes include the instruction set, the number of bits to represent various data I/O mechanisms, and technique for addressing memory. Whereas, organization attributes include those hardware details transparent to the programmer, such as control signals, interfaces between the computer and peripherals, and the memory technology used.

In computer science and engineering, computer architecture is the practical art of defining the structure and relationship of the subcomponents of a computer. As in designing the architecture of buildings, *architecture* can comprise many levels of information. Computer architecture is primarily logical, positing a conceptual system that serves a particular purpose. Computer organization helps optimize performance-based products.

#### Differences between computer organization and architecture:

Computer organization is how operational attributes are linked together and contribute to realize the architectural specifications. Computer architecture is the architectural attributes like physical address memory, CPU and how they should be made and made to coordinate with each other keeping the future demands and goals in mind.

A computer's architecture is its abstract model and is the programmer's view in terms of instructions, addressing modes and registers. A computer's organization expresses the realization of the architecture. Architecture describes what the computer does and organization describes how it does it.

#### **Check your progress**

- 1. Define a computer. How is it classified based on its input?

- 2. What are the types of computers?

- 3. Explain the important operations performed by a computer using the functional units.

- 4. What is the function of a program counter and an instruction register?

- 5. What is the difference between computer organization and architecture?

#### **1.6 SUMMARY**

A computer is said to be operational as a system, when its functional units are interconnected by a group of wires called Bus. One can choose his computer system based on his requirements. And a comfortable choice can be made depending on one's needs related to the cost or speed. In this unit we discussed about functional units of computer, basic operational concepts, definition of organization and architecture.

#### **1.7 KEYWORDS**

**Computer:** A computer is a programmable device that receives input, stores and manipulates data, communicates data and provides output in a suitable format. **Instruction:** An explicit command given to a computer.

**Register:** A high speed storage element.

**Program:** A sequence of instructions stored in memory and processed by a processor.

Analog: data in analog or time varying form for processing.

Digital: data in digital or time invariant form for processing.

| 1.8 ANSWERS TO CHECK YOUR PROGRESS |  |

|------------------------------------|--|

- 1. 1.2 2. 1.2 3. 1.3 4. 1.4

- 5.1.5

# **1.9 UNIT-END EXERCISES AND ANSWERS**

- 1. How are computers classified based on their size, cost, computational power and indented use?

- 2. Name the functional units of a computer and describe its functions.

- 3. How does the CPU interact with the main memory? Explain with necessary block diagram.

- 4. Differentiate between computer organization and architecture.

#### Answers: SEE

- 1. 1.2

- 2. 1.3

- 3. 1.4

- 4. 1.5

#### 1.10 SUGGESTED READINGS

- Carl Hamacher, Zvonko Vranesic, Safwat Zaky: Computer Organization, 5<sup>th</sup> Edition, TMH 2002.

- 2. William Stallings: Computer Organization and Architecture, 7<sup>th</sup> Edition, PHI 2006.

- Vincenet P. Heuring and Harry F. Jordan: Computer Systems Design and Architecture, 2<sup>nd</sup> Edition, Pearson Education, 2004.

# **UNIT 2: COMPUTER STRUCTURES**

#### Structure

- 2.0 Objectives

- 2.1 Introduction

- 2.2 Computer function

- 2.3 Interconnection structures

- 2.4 Bus interconnection

- 2.5 Memory locations, Addressing and Encoding of information.

- 2.6 Summary

- 2.7 Key words

- 2.8 Answers to check your progress

- 2.9 Unit-end exercises and answers

- 2.10 Suggested readings

# 2.0 OBJECTIVES

At the end of this unit you will be able to

- Computer functions

- Define a Bus

- Discuss the various Bus structures

- Memory arrangement

- Addressing and Encoding of information

# **2.1 INTRODUCTION**

This unit is about the computer structures. It describes Computer function, their Interconnection structures. It defines Bus interconnection. It shows how various parts of a computer are interconnected with bus structure. It also deals with Memory locations, Addressing and Encoding of information.

#### 2.2 COMPUTER FUNCTIONS

The main function of a computer is to run programs. The computers are used today for an almost unlimited range of applications. However, irrespective of the application for which a computer is used we can identify a few basic functions that are performed by all computers. All the computer applications make use of these basic functions of computers in different ways and combinations. There are basically four basic functions of computers. They are input, storage, processing and output. These are described below:

- INPUT: This is receiving or accepting information from outside sources. We input data and instructions through input devices which are keyboard, mouse, scanner, etc. The most common way of performing input function is through the information entered through the keyboard and the click of mouse. Of course, there are many other types of devices for receiving such information for example, the web cam. Computers are also able to receive information stored in other devices like DVD disks and pen drives. Computers are also able to receive information from other computers and similar devices. When we use computers for automatic control of machines and processes, computers can also receive information directly from such equipments and processes.

- PROCESSING: The computer processes data. This is really the core of computer operation. The computer processes the data that is fed to the computer by various means and the data already contained in internal memory to produce the results that is the core of all computer applications, which is done by the Central Processing Unit (CPU).

- 3. OUTPUT: After processing the data the computer gives the result as an output. Output devices are the monitor (in the case of visual output), speakers (in the case of audio output), printers, etc. The results of the processing are made available for use by any user or other devices. When a computer is connected to other devices,

including through Internet, this output is in the form of electrical pulses. The output data can also be recorded on to an external recording medium such as a DVD disk.

4. STORAGE-: We can save our data for future use in the computer itself. There are several storage devices also like removable disks, CDs, etc. The information in the computer is stored in computer in several different ways depending on how the information is used. For simplicity we will classify in two broad categories. First is the memory in the central processing unit of the computer, and second is the auxiliary memory. The auxiliary memory includes devices such as fixed hard drives.

#### 2.3 INTERCONNECTION STRUCTURES

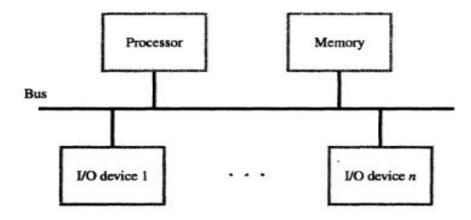

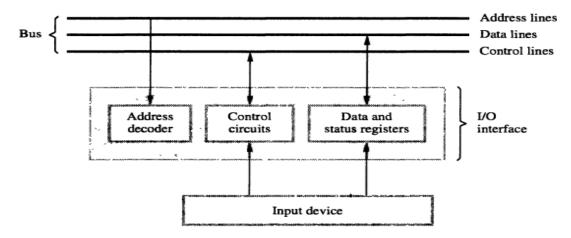

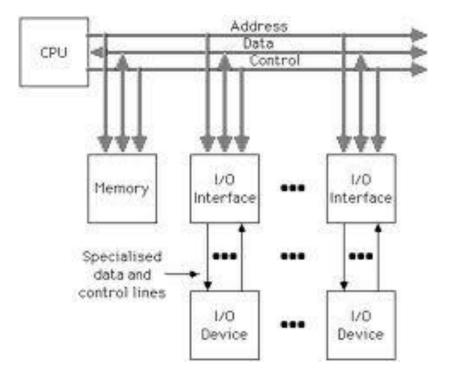

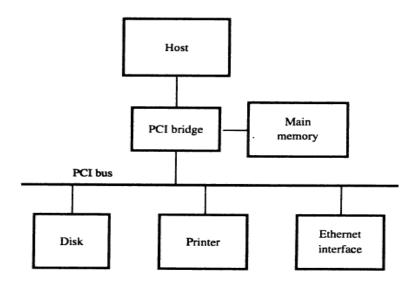

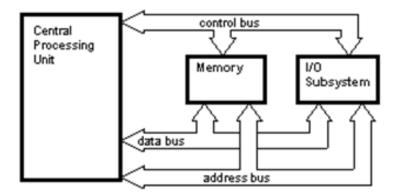

A Computer consists of a set of components (CPU, I/O, memory) that communicates with each other. Collection of paths connecting various computer components is known as Interconnection Structures. The design of this structure will depend on the exchange that must be made between modules. The various types of exchanges/transfers are: Memory to CPU, CPU to Memory, I/O to CPU, CPU to I/O, I/O to or from Memory (Direct Memory Access (DMA)).

#### 2.4 BUS INTERCONNECTION

**Bus:** A Bus is a collection of wires or distinct lines meant to carry data, address and control information. The functional components of a computer must be connected inorder to make a system operational. The connections can be made in several ways using a Bus.

- **Data Bus**: it is used for transmission of data. The number of data lines corresponds to the number of bits in a word.

- Address Bus: it carries the address of the main memory location from where the data can be accessed.

• **Control Bus:** it is used to indicate the direction of data transfer and to coordinate the timing of events during the transfer.

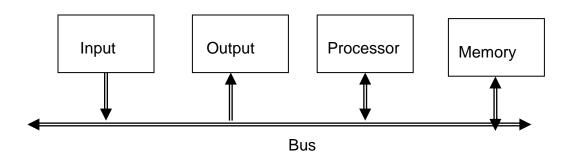

The different functional units of a computer can be connected through a bus structure such as:

- A Single-bus structure

- A Two-bus structure

#### **SINGLE-BUS STRUCTURE:**

All units are connected to a single bus as shown in Figure 2.1. The bus can be used for only one transfer at a time since only two units can actively use the bus at any given instant of time. When multiple requests arise for the use of bus, then the Bus control lines are used for managing it. The primary advantage of this structure is its low cost and flexibility for attaching peripherals. But the drawback is its low operating speed. This type of structure is mainly found in small computers such as minicomputers and microcomputers.

**Figure 2.1 Single-bus Structure**

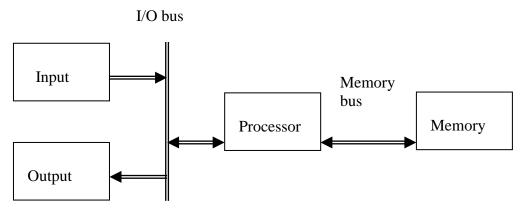

# **TWO-BUS STRUCTURE:**

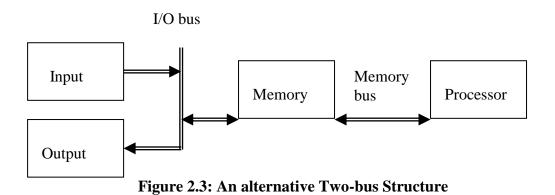

The bus is said to perform two distinct functions by connecting the I/O units with memory and processor unit with memory. The processor interacts with the memory through a memory bus and handles input/output functions over I/O bus. The I/O transfers are always under the direct control of the processor, which initiates transfer and monitors their progress until completion. The main advantage of this structure is good operating speed but on account of more cost.

The Figure 2.2 shows the two-bus structure and Figure 2.3 shows the alternate arrangement of two-bus structure.

Figure 2.2 Two-bus Structure

## AN ALTERNATIVE TWO-BUS STRUCTURE:

Here the positions of memory and processor are interchanged. I/O transfers are directly made to or from the memory. So, special purpose processor called peripheral processor is used for providing the necessary controls over the actual data transfer.

2.5 MEMORY LOCATIONS, ADDRESSES, AND INFORMATION ENCODING

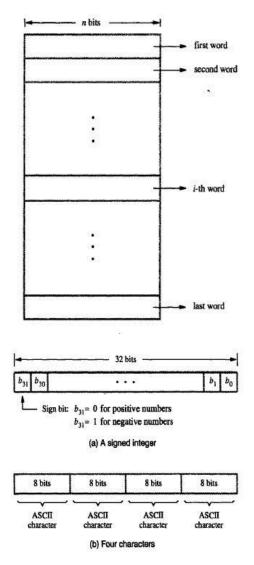

We now discuss the way the programs are executed in a computer from the programmer's point of view. Number and character operands, as well as instructions, are stored in the memory of a computer.

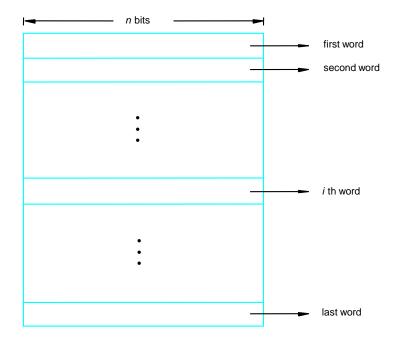

The memory consists of many millions of storage cells, each of which can store a bit of information having the value 0 or 1. Because a single bit represents a very small amount of information, the bits are normally not handled individually. The usual approach is to deal with them in groups of fixed size. For this purpose, the memory is organized so that a group of m bits can be stored or retrieved in a single, basic operation. Each group of m bits is referred to as a word of information, and m is called the word length. The memory of a computer can be schematically represented as a collection of words as shown in Figure 2.4. Modern computers have word lengths that typically range from 16 to 64 bits. If the word length of a computer is 32 bits, a single word can store a 32-bit 2's complement number or four ASCII characters, each occupying 8 bits. A unit of 8 bits is called a byte. Accessing the memory to store or retrieve a single item of information, either a word or a byte, requires distinct addresses for each item location. It is customary to use numbers from 0 through  $2^{n}$  -1. for some suitable values of n, as the addresses of successive locations in the memory. The  $2^n$  addresses constitute the address space of the computer, and the memory can have up to  $2^n$  addressable locations. A 32-bit address creates an address space of  $2^{32}$  or 4G (4 Giga) locations.

Figure 2.4: Main Memory Addresses

#### BYTE ADDRESSABILITY:

We now have three basic information quantities to deal with: the bit, byte and word. A byte is always 8 bits, but the word length typically ranges from 16 to 64 bits. The most practical assignment is to have successive addresses refer to successive byte. Contents of the memory locations can represent either instructions or operands. Operands can be either numbers or characters.

#### **Representation of Numbers in main memory:**

Consider a 32 bit pattern to represent a signed integer. Figure 2.5 shows how a number can be stored in a 32 bit word.

32 bits

| b <sub>31</sub> | b <sub>30</sub> | ••• | b <sub>1</sub> | b <sub>0</sub> |

|-----------------|-----------------|-----|----------------|----------------|

|-----------------|-----------------|-----|----------------|----------------|

Sign bit:  $b_{31} = 0$  for positive numbers

$\mathbf{b}_{31} = \mathbf{1}$  for negative numbers

Magnitude =  $b_{30} \cdot 2^{30} + b_{29} \cdot 2^{29} + \ldots + b_1 \cdot 2^1 + b_0 \cdot 2^0$

#### Figure 2.5: A signed integer

Magnitude can range from 0 to  $2^{31} - 1$  and the numbers are said to be in binary positional notation. The above encoding format is called Signed Magnitude representation. The other two binary representations are 1's compliment and 2's compliment representations. Representation of positive numbers is the same in the three cases. The difference is only in the negative number. In all the three methods the left most bit is the sign bit (i.e.0 represents positive number and 1 represents negative number). 2's compliment method is the most suitable one and is used in all modern computers.

#### **Representation of Characters in main memory**

Characters can be letters of the alphabet, decimal digits, punctuation marks etc. They are represented by codes that are usually 6 - 8 bits long. Figure 2.6 shows how 4 characters in ASCII can be stored in a 32 bit word.

| 8 bits    | 8 bits    | 8 bits    | 8 bits    |

|-----------|-----------|-----------|-----------|

| ASCII     | ASCII     | ASCII     | ASCII     |

| Character | Character | Character | character |

Figure: 2.6: A character

#### **Representation of Instructions in main memory**

A main memory word can also be used to represent an instruction. One part of the word specifies the operation to be performed and the other part specifies operand address. Each of these parts is called as 'field', represented as shown in Figure 2.7

| 8 bits          | 24 bits                |

|-----------------|------------------------|

| Operation field | Addressing information |

# Fig 2.7: An instruction

Here the 8 bit operation field can encode 2<sup>8</sup> (256) distinct instructions. Addressing information is given in a variety of ways. The different ways in which operands can be named in machine instructions are called addressing modes. Memory words whose addresses are specified by the instructions are interpreted as operands. Whether an operand is a character or a numeric data item is determined by the operation field of the instruction. An operand may be either shorter or longer than one word. An operand length of 8 bit is convenient, because this size is used to encode character data.

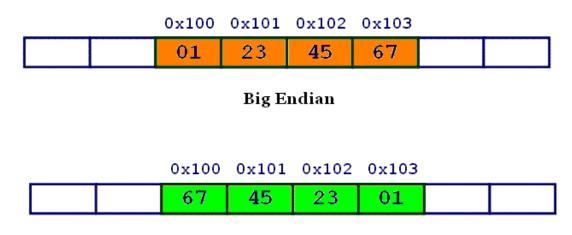

# **BIG-ENDIAN AND LITTLE ENDIAN ASSIGNMENTS**

Little and big-endian are two ways of storing multibyte data-types (int, float, etc). In little-endian machines, last byte of binary representation of the multibyte data-type is stored first. On the other hand, in big-endian machines, first byte of binary representation of the multibyte data-type is stored last.

Suppose integer is stored as 4 bytes (assuming integer is 2 bytes) then a variable x with value  $0 \times 01234567$  will be stored as following.

Little Endian

## **Check your progress**

- 1. What are functions of a computer?

- 2. What are interconnection structures?

- 3. Explain Bus interconnection structure.

- 4. Explain the structure of main memory.

- 5. What is big-endian and little-endian?

# SUMMARY

This unit dealt with the computer structures. It described Computer functions, their Interconnection structures. It also defined Bus interconnection. It also dealt with Memory locations, Addressing and Encoding of information.

# 2.6 KEYWORDS

.

**Interconnection Structures:** Collection of paths connecting various computer components.

**Bus**: A collection of wires or distinct lines meant to carry data, address and control information.

Addressing mode: The different ways, in which operands can be named in machine instructions.

# 2.7 ANSWERS TO CHECK YOUR PROGRESS

- 1 2.2

- 2 2.3

- 3 2.4

- 4 2.5

- 5 2.5

#### 2.8 UNIT-END EXERCISES AND ANSWERS

- 5. What are different types of buses?

- 6. Explain various types of Bus interconnection.

- 7. Describe the structure of main memory.

- 8. With example, distinguish between big-endian and little-endian.

#### **Answers: SEE**

- 1. 2.4

- 2. 2.4

- 3. 2.5

- 4. 2.5

#### 2.9 SUGGESTED READINGS

- Carl Hamacher, Zvonko Vranesic, Safwat Zaky: Computer Organization, 5<sup>th</sup> Edition, TMH 2002.

- 2. William Stallings: Computer Organization and Architecture, 7<sup>th</sup> Edition, PHI 2006.

- Vincenet P. Heuring and Harry F. Jordan: Computer Systems Design and Architecture, 2<sup>nd</sup> Edition, Pearson Education, 2004.

#### **UNIT 3: Main Memory Operations**

#### Structure

- 3.0 Objectives

- 3.1 Introduction

- 3.2 Main memory operations

- 3.3 Instructions and instructions sequencing

- 3.4 Instruction execution and straight-line sequencing.

- 3.5 Condition codes.

- 3.6 Summary

- 3.7 Key words

- 3.8 Answers to check your progress

- 3.9 Unit-end exercises and answers

- 3.10 Suggested readings

# **3.0 OBJECTIVES**

At the end of this unit you will be able to

- Identify main memory operations

- Explain instructions fetch and instructions execution.

- Identify various instruction formats.

- Understand different addressing techniques.

# 3.1 INTRODUCTION

After knowing the general concepts of computer organization and the way computer operates, in this unit, we will see the main memory operations, various types of instructions and instructions sequencing. It also deals with instruction execution and straight-line sequencing, condition codes.

#### 3.2 MAIN MEMORY OPERATIONS

To execute an instruction the instructions must be transferred from the main memory to the CPU.

This is done by the CPU control circuits. Operands and results must also be moved between the main memory and the CPU. Thus two basic operations involving the main memory are needed namely, **Load (or Fetch or Read) and Store (or Write).**

**Load operation:** Transfers a copy of the contents of a specific memory location to the CPU. The Word in the main memory remains unchanged. To start a Load or Fetch operation, CPU sends the address of the desired location to the main memory and requests to read its contents. The main memory reads the data stored at that address and sends them to the CPU.

**Store operation:** Transfers a word of information from the CPU to a specific main memory location, destroying the former contents of that location. Here the CPU sends the address of the desired location to the main memory, together with the data to be written to that location.

#### **3.3 INSTRUCTIONS AND INSTRUCTION SEQUENCING**

A computer must have instructions capable of performing four types of operations

- 1. Data transfers between the main memory and the CPU registers

- 2. Arithmetic and logic operations on data

- 3. Program sequencing and control

- 4. I/O transfers

#### Notations used:-

**a) Register Transfer Notation (RTN):-** Possible locations involved in transfer of information are memory location, CPU registers or registers in the I/O subsystem. We

identify the names for the addresses of memory location as LOC, PLACE, A, VAR2 etc and the names for CPU registers as R0, R5 etc. The contents of a location or a register are denoted by placing the corresponding name between square brackets.

E.g. i) R1 \_ [LOC] means that the contents of memory location LOC are transferred into register R1.

ii) R3  $_$  [R1] + [R2] adds the contents of registers R1 and R2 and then places their sum into register R3.

**b) Assembly Language Notation:-** The same operations can be represented in assembly language format as shown below.

E.g. i) Move LOC, R1 ii) Add R1,R2,R3

# **BASIC INSTRUCTION TYPES**

There are five types of instruction formats in a computer that are commonly used, namely:

- 1. Three-address instruction format

- 2. Two-address instruction format

- 3. One-address instruction format

- 4. Zero-address instruction format

- 5. One-and-half address instruction format

# **Three-address instruction**

C = A + B is a high level instruction to add the values of the two variables A and B and to assign the sum to a third variable C. When this statement is compiled, each of these variables is assigned to a location in the memory. The contents of these locations represent the values of the three variables. Hence the above instruction requires the action:

# $C_{-}[A] + [B]$

To carry out this instruction, the contents of the memory locations A and B are fetched from the main memory and transferred into the processor – sum is computed – result is

sent back to memory and stored in location C. The same action is performed by a single machine instruction (three address instruction)

Add A,B,C

Operands A and B are called the *source operands*, C is called the destination operand, and Add is the operation to be performed on the operands. The general format is

Operation Source1, Source2, Destination

If k bits are needed to specify the memory address of each operand, the encoded form of the above instruction must contain 3k bits for addressing purposes + the bits needed to denote the Add operation.

#### **Two-address instruction**

An alternative method is to use two address instruction of the form

**Operation Source, Destination**

E.g. Add A,B which perform the operation

$B_{-}[A] + [B]$  Here the sum is calculated and the result is stored in location B replacing the original contents of this location. i.e. operand B acts as source as well as destination. In the former case (three address instruction) the contents of A and B were not destroyed. But here the contents of B are destroyed. This problem is solved by using another twoaddress instruction to copy the contents of one memory location into another location.

Now C \_ [A] + [B] is equivalent to Move B,C Add A,C

Note: In all the above instructions, the source operands are specified first, followed by the destination. But there are many computers in which the order is reversed.

#### **One-address instruction**

Instead of mentioning the second operand, it is understood to be in a unique location. A processor register usually called the **Accumulator** is used for this purpose.

E.g. i) Add A means that the contents of the memory location A is added to the contents of accumulator and places the sum in the accumulator.

ii) Load A copies the contents of memory location A into accumulator

iii) Store A copies the contents of accumulator to the location A

Depending on the instruction, the operand may be source or destination.

Now the operation  $C_{[A]} + [B]$  can be performed by executing the following instructions

Load A Add B Store C

The above mentioned instructions can also be handled by using general purpose registers. Let R*i* represent a general purpose register.

Move A,R*i* Move R*i*,A Add A,R*i*

They are generalizations of Load, Store and Add instructions of the single accumulator case in which register R*i* performs the functions of accumulator.

When a processor has several general-purpose registers, then many instructions involve only operands that are in registers.

E.g., Add R*i*, R*j* Add R*i*, R*j*, R*k*

In the first instruction, Rj acts as both source and destination. In the second instruction,

Ri

And  $R_j$  are source and  $R_k$  is the destination.

#### Advantages of using CPU registers:

i) Data access from these registers is faster than that of main memory locations; because these registers are inside the processor.

ii) Only few bits are needed to specify the register; because the number of registers is very less.

For example, only 5 bits are needed to specify 32 registers.

iii) Instructions, where only register names are contained, will normally fit into one word of memory.

#### **Zero-address instruction**

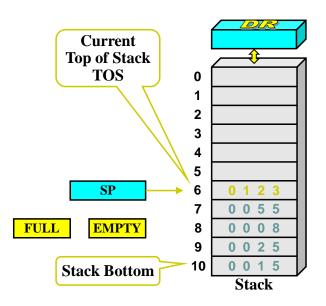

Here locations of all operands are defined implicitly. Such instructions are found in machines that store operands in a structure called a *pushdown stack*. A stack is a list of data elements, usually words or bytes, in which these elements can be added or removed through the top of the stack by following the LIFO (last-in-first-out) storage mechanism. A processor register called **stack pointer**. (**SP**) is used to keep track of the address of the element at the top of the stack at any given time. The terms **push** and **pop** are used to describe placing a new item on the stack and removing the top item from the stack respectively.

## One and half-address instruction

An instruction that specifies one operand in memory and one operand in a CPU register is referred to as one-and-half address instruction. Using registers it is possible to increase the speed of processing.

# 3.4 INSTRUCTIONS EXECUTION AND STRAIGHT LINE SEQUENCING

# **3.4.1 STRAIGHT LINE SEQUENCING**

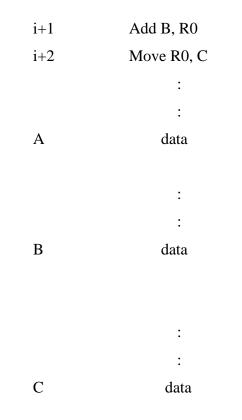

Let us take the operation  $C \leftarrow [A] + [B]$ . The Example 3.1 shows the program segment as it appears in the main memory of a computer that has a two-address instruction format and a number of general purpose CPU registers.

# Example 3.1 A program for $C \leftarrow [A] + [B]$

Address

Contents

| Begin execution here $\rightarrow$ | i | Move A,R0 | ; A, B, A are memory |

|------------------------------------|---|-----------|----------------------|

| locations                          |   |           |                      |

For executing this program, the following steps are to be performed.

1. CPU contains the register called PC which holds the address of the instruction to be executed next. To begin execution, the address of the first instruction 'i' must be placed in PC.

2. CPU control circuits use the information in the PC to fetch and execute the instructions one at a time in the increasing order of addresses. This is called straight line sequencing.

3. As each instruction is executed, the PC is incremented by 4 to point to the next instruction.

Executing a given instruction is a two-phase procedure.

**First Phase - Instruction Fetch:** Instruction is fetched from the main memory location whose address is in the PC and is placed in the Instruction Register (IR)

**Second Phase – Instruction Execute:** Instruction in the IR is examined to determine which operation is to be performed. The specified operation is performed by the processor. This may involve fetching operands from main memory (or processor registers), performing an arithmetic or logic operation and storing the result in the destination location. At some point during this two-phase procedure, the contents of the PC are advanced to point to the next instruction. After the execution phase is over, new instruction fetch can begin.

#### **3.4.2 BRANCHING**

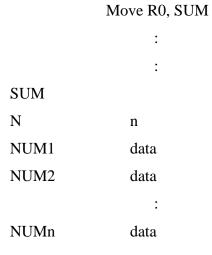

Consider the task of adding 'n' numbers. Let the address of memory locations containing n numbers are NUM1, NUM2,...NUM*n*. Separate Add instruction is used to add each number to the contents of register R0. After all the numbers have been added, the result is placed in the memory location SUM.

#### Example 3.2 A straight-line program for adding *n* numbers

|                                    | Address |      | Contents |

|------------------------------------|---------|------|----------|

|                                    |         |      |          |

| Begin execution here $\rightarrow$ | i       | Move | NUM1,R0  |

|                                    | i+1     | Add  | NUM2, R0 |

|                                    | i+2     | Add  | NUm3, R0 |

|                                    |         |      | :        |

|                                    |         |      | :        |

|                                    | i+n-1   | Add  | NUMn, R0 |

|                                    | i+n     | Move | R0, SUM  |

|                                    |         |      | :        |

|                                    |         |      | :        |

|                                    | SUM     | da   | ıta      |

|                                    | NUM1    | dat  | a        |

|                                    | NUM2    | dat  | a        |

NUMn

: data

Instead of using long list of Add instruction, it is possible to place a single Ad instruction in a loop as shown in Example 3.3 This loop causes a straight line sequence of instructions to be executed repeatedly. The loop starts at location LOOP and ends at the instruction Branch>0. During each pass through this loop, the address of the next entry is determined and that entry is fetched and added to R0. Assume that the number of entries in the list '*n*' is stored in location N as shown.

Register R1 is used as a counter to determine the number of time the loop is to be executed. Hence the contents of the location N are loaded in register R1 at the beginning of the program. Then within the body of the loop the instruction

Decrement R1 reduces the contents of R1 by 1 each time through the loop. This means that execution of the loop must be repeated as long as the result of the decrement operation is greater than 0.

#### Example 3.3 Using a loop to add *n* numbers.

Address

Contents

Move N,R1

Clear R0

Loop: Determine address of "Next" number and add "Next" number

to R0

Decrement R1 Branch > 0 Loop Move R0,SUM : : Add NUMn, R0

We now introduce Branch instruction. This type of instruction loads a new value into the program counter. As a result, the processor fetches and executes the instruction at this new address. A conditional branch instruction causes a branch only if a specified condition is satisfied. If the condition is not satisfied, the PC is incremented in the normal way and the next instruction in sequential address order is fetched and executed.

# 3.5 CONDITION CODES

The processor keeps track of some information about the results of various operations for use by subsequent conditional branch instructions. This is done by recording the required information into individual bits called as *condition code flags*. In some processors, these flags are grouped together in a special register called the *condition code register* or *status register*.

Four commonly used flags are:-

N (negative) Sets to 1 if the result is negative; otherwise, cleared to 0

Z (zero) Sets to 1 if the result is 0; otherwise, cleared to 0

V (overflow) Sets to 1 if arithmetic overflow occurs; otherwise, cleared to 0

C (carry) Sets to 1 if carry-out results from the operation; otherwise, cleared to 0

## **Check your progress:**

- 1. Explain the memory operations.

- 2. Explain the different types of instruction format that are commonly used in a computer.

# 3.6 SUMMARY

This unit introduced memory operations, various instructions, its representation in different formats. The principles of instructions execution were emphasized. With the understating of this, a reader can do detailed study of instruction execution of any computer architecture.

# 3.7 KEYWORDS

**Instruction:** It is basic step to instruct a computer to carry out. A program consists of a sequence of these steps.

# 3.8 ANSWERS TO CHECK YOUR PROGRESS

- 1.3.2

- 2.3.3

# 3.9 UNIT-END EXERCISES AND ANSWERS

- 9. Explain the classification of instructions.

- 10. What is zero-address and one-and-half address instruction format? Explain their uses.

- 11. Explain the phases of an instruction execution.

- 12. Name the flags used with condition codes.

## **Answers: SEE**

- 1. 3.3

- 2. 3.3

- 3. 3.4

- 4. 3.5

# 3.10 SUGGESTED READINGS

- Carl Hamacher, Zvonko Vranesic, Safwat Zaky: Computer Organization, 5<sup>th</sup> Edition, TMH 2002.

- 2. William Stallings: Computer Organization and Architecture, 7<sup>th</sup> Edition, PHI 2006.

- Vincenet P. Heuring and Harry F. Jordan: Computer Systems Design and Architecture, 2<sup>nd</sup> Edition, Pearson Education, 2004.

# UNIT 4: ADDRESSING MODES AND ASSEMBLY LANGUAGE

## Structure

- 4.1 Objectives

- 4.1 Introduction

- 4.2 Addressing modes

- 4.3 Assembly languages

- 4.4 Assembler directives, Assembly and execution of programs

- 4.4 Stacks and queues

- 4.5 Number representation and operations.

- 4.6 Summary

- 4.7 Key words

- 4.8 Answers to check your progress

- 4.9 Unit-end exercises and answers

- 4.10 Suggested readings

# 4.0 **OBJECTIVES**

At the end of this unit you will be able to

- Identify the definition of addressing mode

- Examine and use different addressing techniques

- define what is an assembler, a source program, an object program

- explain what is an assembly language and its the importance in programming

- explain assembly language programs and the manner in which it gets executed

- use and appreciate binary number notation in assembly language programming

- Stacks and queues

- Number representation and operations

# 4.1 INTRODUCTION

This unit is about the addressing modes and assembly languages. Machine instructions are represented by strings of 0's and 1's. Such patterns of 0's and 1's become

cumbersome while programs are discussed or written. So, these patterns are represented and replaced by symbolic names. Some examples of symbolic names include Move, Add, Branch, Increment etc. When writing programs for a specific computer, the symbolic names are replaced by acronyms called mnemonics. Examples of mnemonics include MOV, ADD, BR, INC etc. Using mnemonics and Register Transfer Notation, a program is written governing the rules. Such a program is called as an assembly language. The set of rules for using the mnemonics in the specification of complete instructions and programs is called the syntax of the language.

#### 4.2 ADDRESSING MODES

The term addressing mode refers to the way in which the operand of an instruction is specified.

**1.** *Register mode:* The operand is the contents of a CPU register; the name of register is given in the instruction

E.g. Move R1,R2 The contents of R1 is transferred to R2

**2.** *Absolute mode (Direct mode):* The operand is in a memory location. The address of the memory location is explicitly given in the instruction.

E.g. Add A,B The contents of the memory location A is added to the contents of the memory location B. The addresses of A and B are given in the instruction itself.

**3.** *Immediate mode:* The operand is given explicitly in the instruction. This mode is used in specifying address and data constants in programs

E. g. Move #200, R0

This instruction places the value 200 in register R0.

**4.** *Indirect mode:* Here the instruction does not give the operand or its address explicitly. Instead it provides the effective address of the operand. Effective address of the operand is the contents of a register or main memory location, whose address appears in the instruction. We denote indirection by placing the name of the register or the memory address given in the instruction in parenthesis

Let us consider two cases:

i) Add (A), R0

#### ii) Add (R1), R0

In the first case, when the instruction is executed, CPU starts by fetching the contents of location A in the main memory. Since indirect addressing is used, the value B stored in A is not the operand, but the address of the operand. Hence CPU requests another read operation from the main memory and this is to read the operands (contents of location B). The CPU then adds the operand to the contents of R0

In the second case, the operand is accessed indirectly through register R1 which contains the value B.

*Note:* The register or memory location that contains the address of the operand is called a pointer. Indirection is a powerful concept in programming.

5. *Index mode:* In this mode, the effective address of the operand is generated by adding a constant value to the contents of a register. The register used may be a special register provided for this purpose or may be any one of the general purpose register – referred to as an *Index Register*.

Index mode is indicated symbolically as X(Ri), where X denotes a constant value contained in the instruction and R*i* is the name of the register involved. The effective address of the operand is given by EA or Aeff = X + [R*i*]

In assembly language program, the constant X may be given either as an explicit number or as a name representing a numerical value.

There are two ways of using the index mode.

- Offset is given as a constant: Here the index register R1 contains the address of a memory location and the value X defines an offset called displacement Add 20(R1),R2

- 2. Offset is in the index register: Here the constant X corresponds to a memory address and the contents of the index register define the offset to the operand.

Add 1000(R1),R2

In either case, the effective address is the sum of two values; one is given explicitly in the instruction and the other is in a register.

5. *Relative mode:* The effective address is determined by the index mode. But here the program counter (PC) is used in place of the general purpose register  $R_i$ . i.e. X(PC) can be used to address a memory location that is X bytes away from the location presently pointed by the program counter. Since the addressed location is identified "relative" to the program counter, which always identifies the current execution point in a program, this mode is called as Relative mode.

This mode is used to access data operands. It is commonly used to specify the target address in branch instruction.

**6.** *Autoincrement mode:* The effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of the register is automatically incremented to point to the next item in a list. We denote the autoincrement mode by putting the specified register in parenthesis to show that the contents of register is used as the effective address, followed by a plus (+) sign to indicate that these contents are to be incremented after the operand is accessed. Thus the autoincrement mode is written as

(Ri) +. If we use autoincrement mode, it is possible to eliminate the increment instruction

7. Autodecrement mode: The contents of a register specified in the instruction are decremented. These contents are then used as the effective address of the operand. We denote the

autodecrement mode by putting the specified register in the parenthesis, preceded by a minus (-) sign to indicate that the contents of the register are to be decremented before being used as the effective address. Thus we write - (R4). This mode allows accessing of operands in the direction of descending address.

## 4.3 ASSEMBLY LANGUAGES

#### Assembler:

Programs written in assembly level language can be automatically translated into a sequence of machine instructions by a program called an assembler. Assembler is an

important utility program, and it is an example for system software. Like any other program, an assembler is also stored as a sequence of machine instructions in the memory of the computer. A user program is usually entered into a computer with the help of a keyboard and it is either stored in the memory of the computer or on the magnetic disk. So, a user program is simply a set of alphanumeric characters. When the assembler program is executed, it reads the user program, analyzes it and then generates the desired machine language program. The user program in its original alphanumeric text is called as a source program, and the assembled machine language program is called as an object program.

**Note**: the assembly language for a given computer may or may not be case sensitive i.e. it may or may not distinguish between capital and lower case letters.

In our discussions, we will use capital letters to denote all symbolic names and labels. And the instruction format consists of the following:

### **Op-code Operand1, Operand2**

The op-code (or operation code) mnemonic is followed by at least one blank space character and this is followed by the information that specifies the operands separated by comma. Since there are several addressing modes for specifying operand locations, the instruction must indicate this.

#### **Examples:**

#### 1. MOVE R0, SUM

The mnemonic MOVE represents the binary pattern or OP code. This operation move is performed by this instruction. The assembler translates this mnemonic into binary OP code that is computer is capable of understanding. Here R0 is the source operand and SUM is the binary address representation of the destination operand and it is in the memory location.

#### 2. ADD #5, R3

This instruction adds he number 5 to the contents of register R3. The result of this operation is put back in the register R3. # symbol indicates that the addressing mode

followed is immediate mode. Where in, the data value 5 is explicitly specified as a part of instruction. Some assembly language use op-code mnemonic instead of symbols. In such case, the instruction ADDI 5, R3 is used in place of ADD #5, R3 where the suffix I in the mnemonic ADDI states that the source operand is given in the immediate addressing mode.

#### 3. MOVE #5, (R2)

In this instruction, the parentheses around the name or symbol denote a pointer to the operand. Suppose R2 contains MEM1 the address of memory location, then executing this instruction means the number 5 is to be placed in a memory location which is pointed to by register R2. This instruction can also be written as MOVEI 5(R2) where the suffix I in the mnemonic MOVEI states I denotes Indirect mode.

#### 4.4 ASSEMBLER DIRECTIVES

Apart from providing a mechanism for representing instructions in a program, the assembly programming language also allows the programmer to specify other information which is essential to translate the source program into object program. Such statements in a program are called assembler directives or commands. This statement does not denote an instruction that will be executed when the object program is run. As an example let us consider the statement

#### SUM EQU 200

In the above statement, SUM is a name which is used to represent value 200. This statement informs the assembler that the name SUM should be replaced with the value 200 when ever it is called for.

Let us illustrate the use of assembly language through the following program. Here we are considering a 32 bit word length computer and it is byte addressable. The memory arrangement for the program is shown in Figure 4.1.

|                      | А  | .ddress | Contents      |

|----------------------|----|---------|---------------|

| Begin execution here | -  | 100     | Move N,R1     |

|                      |    | 104     | Move#NUM1,R2  |

|                      |    | 108     | Clear R0      |

|                      |    | 112     | Add (R2),R0   |

|                      |    | 116     | Add #4,R2     |

|                      |    | 120     | Decrement R1  |

|                      |    | 124     | Branch>0 LOOP |

|                      |    | 128     | Move R0,SUM   |

|                      |    | 132     |               |

|                      |    |         | •             |

|                      |    |         | •             |

| . SUN                | N  | 200     |               |

| И                    |    | 204     | 100           |

| NUI                  | M1 | 208     |               |

| NUI                  | M2 | 212     |               |

|                      |    |         | •             |

|                      |    |         | •             |

| NUI                  | Mn | 604     |               |

**Figure 4.1 Memory arrangements for the program**

Figure 4.1 shows the memory addresses where the machine instructions and the required data items are to be found after the program is loaded for the execution. The assembler needs to know the information pertaining to questions such as: how to interpret names, where to place the instructions in the memory or where to place the data operands in the memory, if it has to produce an object program for the program. The source program may be written as shown in Figure 4.2 to provide the required information for the assembler with respect to program in Figure 4.1. The use of assembler directives may be seen in example program of Figure 4.2.

|                          | Memory address<br>label | Operation | Addressing or data<br>Information |

|--------------------------|-------------------------|-----------|-----------------------------------|

| Assembler directives     | SUM                     | EQU       | 200                               |

|                          |                         | ORIGIN    | 204                               |

|                          | N                       | DATAWORD  | 100                               |

|                          | NUM1                    | RESERVE   | 400                               |

|                          |                         | ORIGIN    | 100                               |

| Statements that generate | START                   | MOVE      | N,R1                              |

| machine instructions     |                         | MOVE      | #NUM1,R2                          |

|                          |                         | CLR       | RO                                |

|                          | LOOP                    | ADD       | (R2),R0                           |

|                          |                         | ADD       | #4,R2                             |

|                          |                         | DEC       | R1                                |

|                          |                         | BGTZ      | LOOP                              |

|                          |                         | MOVE      | R0,SUM                            |

| Assembler directive      |                         | RETURN    | START                             |

|                          |                         | END       |                                   |

# Figure 4.2 assembly language representations for the program in Figure 4.1

The meaning and importance of the assembler directives used in the example program are given below:

# **1. EQU**

EQU is the Equate directive. It informs the assembler about the value of SUM.

# 2. ORIGIN

This informs the assembler program where in the memory to place the data blocks that follows.

## **3. DATAWORD**

This directive is used to inform the assembler about the data value that needs to be placed in the memory location indicated by ORIGIN directive.

### **4. RESERVE**

This indicates that the specified size of memory block is to be reserved for data. In the example, a memory block of 400 bytes is to be reserved for data and the name NUM1 is to be associated with address 208.

## 5. END

This tells the assembler that this is the end of the source program text. It includes the label START which is the address of the location in which execution of the program is to begin.

### 6. RETURN

This directive identifies the point at which execution of the program should be terminated. It causes the assembler to insert an appropriate machine instruction that returns control to the operating system of the computer.

## 4.5 ASSEMBLY AND EXECUTION OF PROGRAMS

A source program which is written in an assembly language must be assembled into machine language object program before it gets executed. This task is performed by an assembler which replaces all symbols denoting operations and addressing modes with the binary codes used in machine instructions and replaces all names and labels with their actual values. The assembler assigns addresses to instructions and data blocks starting at the address given in the ORIGIN assembler directives. It also inserts constants that may be given in the DATAWORD directives and it reserves memory space as requested by the RESERVE commands.

An important part of the assembly process is to determine the values that replace the names. The value of a name can be specified by an EQU directive or a name can be defined in the Label field of a given instruction. The value represented by the name is determined by the location of the instruction which is currently under consideration in the assembled object program. Hence, the assembler must be able to keep track of addresses as it generates the machine code for successive instructions.

In certain instances, for example when there is a branch instruction in the program, the assembler do not directly replace a name representing an address with the actual value of this address. Instead, it implements the branch instruction by specifying the branch target using relative addressing mode. The assembler computes the branch offset, which is nothing nut the distance to the target and puts it into the machine instruction.

#### **Two-pass assembler:**

An assembler keeps track of all names and numerical values that correspond to them while scanning through a source program with the help of a symbol table. When a name appears for the second time, it is replaced with its value from the symbol table. But, a problem arises when a name appears as an operand before it is given a value. A simple solution to this problem is to have the assembler scan through the source program two times. During the first scan or first pass, it creates a complete symbol table. At the end of this pass, all names are assigned with numerical values. The assembler then goes through the source program for a second time or second pass where in it substitutes values for all names from the symbol table. This kind of assembler with two passes is known as a twopass assembler.

#### Loader:

The assembler stores the object program on a magnetic disk. The object program must be loaded into the memory of a computer before it is being executed. In order to accommodate this, a loader is used. A loader is a utility program placed in memory. Executing the loader performs a sequence of input operations that are needed to transfer the machine language program from the disk into a specified place in the memory. The loader must know the length of the program and the address in the memory where it will be stored. This information is made available by an assembler and it is placed as information in a header preceding the object code. When the object program begins executing, it proceeds to completion unless there are logical errors in the program. And these errors are found out by the users with the help of system software program known as a debugger. This program enables a user to stop execution of the object program at certain points of interest and also to examine the contents of various processor registers and memory locations.

#### 4.6 STACKS AND QUEUES

A stack is an important data structure. It is a list of data items with the accessing restriction that item can be added or removed at one end of the list only. This is called the top of the stack, and the other end is called the bottom. A stack is also called pushdown stack or LIFO data structure. E.g, a pile of trays in cafeteria, the way they are used and placed back. The terms push and pop are used to describe placing a new item on the stack and removing the item from the stack, respectively.

Data stored in the memory of a computer can be organized as a stack, with successive elements occupying successive memory locations. Assume that the first element is placed in location BOTTOM, and when new elements are pushed onto the stack, they are placed in successively lower address locations. We use a stack that grows in the direction of decreasing memory addresses in our discussion, because this is a common practice.

Figure 4.3 A stack of words in the memory.

Figure 4.3 shows a stack of word data items in the memory of a computer. It contains numerical values, with 43 at the bottom and -28 at the top. A processor register is used to keep track of the address of the element of the stack that is at the top at any given time. This register is called the *stack pointer* (SP). It could be one of the general-purpose registers or a register dedicated to this function. The push operation can be implemented as

where the Subtract instruction subtracts the source operand 4 from the destination operand contained in SP and places the result in SP. These two instructions move the word from location NEWITEM onto the top of the stack, decrementing the stack pointer by 4 before the move. The pop operation can be implemented as

Move (SP), ITEM Add #4, SP These two instructions move the top value from the stack into location ITEM and then increment the stack pointer by 4 so that it points to the new top element. If the processor has the Autoincrement and Autodecrement addressing modes, then the push operation can be performed by the single instruction

Move NEWITEM,-(SP)

and the pop operation can be performed by Move (SP)+,ITEM

When a stack is used in a program, it is usually allocated a fixed amount of space in the memory. In this case, we must avoid pushing an item onto the stack when the stack has reached its maximum size. Also, we must avoid attempting to pop an item off an empty stack, which could result from a programming error

Another useful data structure that is similar to the stack is called a *queue*. Data are stored in and retrieved from a queue on a first-in–first-out (FIFO) basis. Thus, if we assume that the queue grows in the direction of increasing addresses in the memory, which is a common practice, new data are added at the back (high-address end) and retrieved from the front (low-address end) of the queue.

There are two important differences between how a stack and a queue are implemented. One end of the stack is fixed (the bottom), while the other end rises and falls as data are pushed and popped. A single pointer is needed to point to the top of the stack at any given time. On the other hand, both ends of a queue move to higher addresses as data are added at the back and removed from the front. So, two pointers are needed to keep track of the two ends of the queue.

Another difference between a stack and a queue is that, without further control, a queue would continuously move through the memory of a computer in the direction of higher addresses. One way to limit the queue to a fixed region in memory is to use a *circular buffer*. Let us assume that memory addresses from BEGINNING to END are assigned to

the queue. The first entry in the queue is entered into location BEGINNING, and successive entries are appended to the queue by entering them at successively higher addresses. By the time the back of the queue reaches END, space will have been created at the beginning if some items have been removed from the queue. Hence, the back pointer is reset to the value BEGINNING and the process continues.

As in the case of a stack, care must be taken to detect when the region assigned to the data structure is either completely full or completely.

#### 4.7 NUMBER REPRESENTATION AND OPERATIONS

While programming using an assembly language it is convenient to use any familiar number representations for representing numerical values. These values are stored in the computer as binary numbers. In some situations, it is more convenient to specify the binary patterns directly. Most of the assemblers allow the programmer to specify numeric values in various ways, using conventions that are defined by the syntax of assembly language.

Let us consider an example, the number 93 which can be represented by an 8-bit binary number 01011101. If this value is to be used as an immediate operand, it can be written as a decimal number as shown in the instruction

#### ADD #93,R1

or as a binary number identified by a prefix symbol such as with a percent sign. It is shown as

### ADD #%01011101, R1

But writing instructions using binary numbers become very cumbersome. So, to make the program development easy and convenient, the binary numbers are written in a compact manner by using hexadecimal number representations. In hexadecimal or hex notation, four bits are represented by a single hex digit. This notation is a direct extension of the Binary Coded Decimal (BCD) code. Where, the numbers 0000, 0001, .....,1001 are represented by the digits 0, 1, ....,9 as in BCD. The remaining six 4-bit patterns 1010, 1011,.....,1111 are represented by letters A, B, ...., F. In hexadecimal representation, the

decimal value 93 becomes 5D and it is often identified by prefixing a dollar sign. Thus the instruction ADD #%01011101, R1 could be written in assembly language with hex notation as

ADD #\$5D,R1

### **Check your progress:**

- 1. Explain the following addressing modes using suitable examples: absolute mode, index mode, immediate mode, relative mode

- 2. What is an assembler?

- 3. With an example, explain the use of assembler directives.

- 4. What is hexadecimal notation? Give examples

## 4.8 SUMMARY

In this unit, the principles of general addressing techniques were emphasized. We were able to see and briefly discuss about the most important system software such as an assembler and a loader. An assembler translates the assembly language program into machine language. Using mnemonics it is possible to write assembly language programs. Further, assembler directives or commands are used by the programmers for specifying other information to an assembler for translating the source program into object program. The manner in which an assembly language program is written and executed is briefly discussed in this unit along with the importance of representing numerical values in hex notation.

## 4.9 KEY WORDS

Addressing mode: The method used to provide an access path to operands in memory and CPU registers.

Effective address: The address generated by the CPU to access the operands in memory

**Mnemonics**: Symbolic names or acronyms used for representing patterns of 0's and 1's in an instruction.

**Assembly Language**: Is a programming language with a complete set of mnemonics and the rules for using it.

**Assembler**: Is a program which translates the program written in assembly language into a sequence of machine instructions.

Source program: The user program in its original alphanumeric text format.

**Object program:** The assembled machine language program.

**Assembler directives:** Directives or commands used by the assembler while it translates a source program into an object program.

# 4.10 ANSWERS TO CHECK YOUR PROGRESS

- 1. 4.2

- 2. 4.3

- 3. 4.4

- 4. 4.7

# 4.11 UNIT-END EXERCISES AND ANSWERS

- 1. What is autoincrement mode? When do you use it?

- 2. What are mnemonics? Give examples.

- 3. Define the following: Source program, object program, assembler

- 4. Explain the following assembler directives: ORIGIN, DATAWORD, RESERVE

- 5. What is a two-pass assembler? Explain the importance of each phase.

- 6. What is the function of: loader, debugger

- 7. Expand BCD.

# Answers: SEE

- 1. 4.2

- 2. 4.1

- 3. 4.3

- 4. 4.4

5. 4.5

- 6. 4.5

- 7. 4.7

# 4.12 SUGGESTED READINGS

- 1. Carl Hamacher, Zvonko Vranesic, Safwat Zaky: **Computer Organization**, 5<sup>th</sup> Edition, TMH 2002.

- 2. William Stallings: Computer Organization and Architecture, 7<sup>th</sup> Edition, PHI 2006.

- Vincenet P. Heuring and Harry F. Jordan: Computer Systems Design and Architecture, 2<sup>nd</sup> Edition, Pearson Education, 2004.

# **UNIT 5: FUNDAMENTAL CONCEPTS**

## Structure

- 5.0 Objectives

- 5.1 Introduction

- 5.2 Some Fundamental Concepts

- 5.2.1 Fetching a word from Memory

- 5.2.2 Storing a Word in Memory

- 5.2.3 Register Transfer

- 5.2.4 Performing Arithmetic or Logic operations

- 5.2.5 Register Gating and Timing of Data Transfers

- 5.3 Execution of a Complete Instruction

- 5.3.1 Branch Instruction

- 5.4 Summary

- 5.5 Key words

- 5.6 Answers to check your progress

- 5.7 Unit-end exercises and answers

- 5.8 Suggested readings

# 5.0 **OBJECTIVES**

At the end of this unit you will be able to

- Understand some Fundamental concepts such as

- Register transfers

- Performing an Arithmetic or Logic Operation

- Fetching a word from memory and storing a word in memory

- Understand execution of a complete instruction

- Explain branch instruction

## 5.1 INTRODUCTION

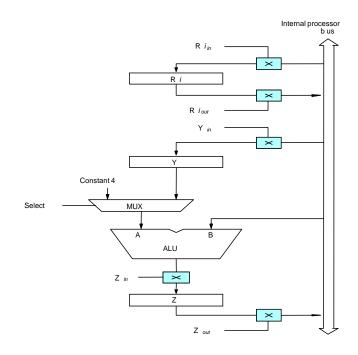

This unit is about the processing unit, which executes machine instructions and coordinates the activities of other units. This is also called a processor or instruction set processor (ISP). We understand its internal structure and how it performs the tasks of fetching, decoding, and executing instructions of a program. The processing unit is called central processing unit (CPU). We explore the organization of the hardware that enables a CPU to perform its main function. We learn how the execution of a complete instruction takes place and we also learn Branch Instructions.

## 5.2 SOME FUNDAMENTAL CONCEPTS

A program, a set of instructions, to be executed by a computer is loaded in sequential locations in the main memory. To execute this program, the CPU fetches one instruction at a time and performs the functions specified. Until a branch or a jump instruction is executed, instructions are fetched from successive memory locations. The address of the next instruction to be executed is kept by the CPU in a dedicated register called program counter (PC). The contents of the PC are updated to point to the next instruction in the sequence.

Assume that each instruction occupies one memory word. Therefore, one instruction execution requires the CPU to perform the following 3 steps:

Fetch the contents of the memory location by the PC into instruction register (IR). Symbolically, this can be written as:

$IR \leftarrow [[PC]]$

2. Increment the contents of the PC by 1, i.e., (assuming word addressable)

- $PC \leftarrow [PC]+1$

- 3. Carry out the actions specified by the instruction in the IR.

Steps 1 and 2 are called the fetch phase and step 3 is called the execution phase.

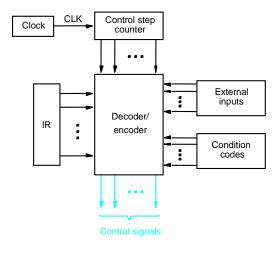

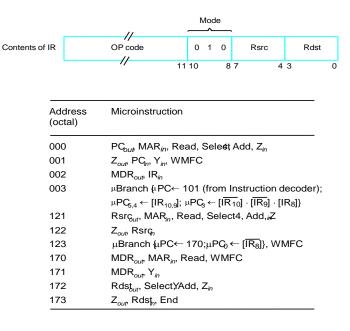

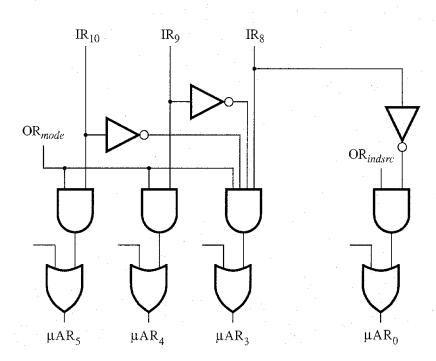

Figure 5.1 Single-bus Organization of the Datapath inside a processor

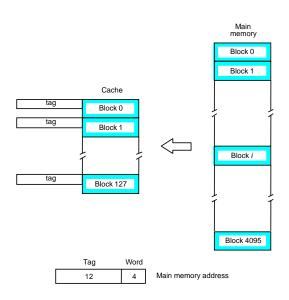

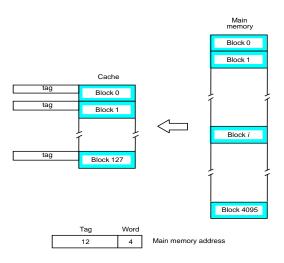

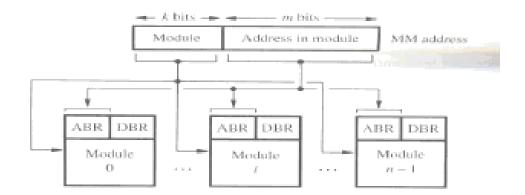

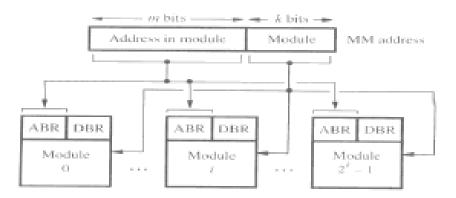

Figure 5.1 shows an organization in which the arithmetic and logic unit (ALU) and all the registers are interconnected via a single common bus. This bus is internal to the processor.